-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

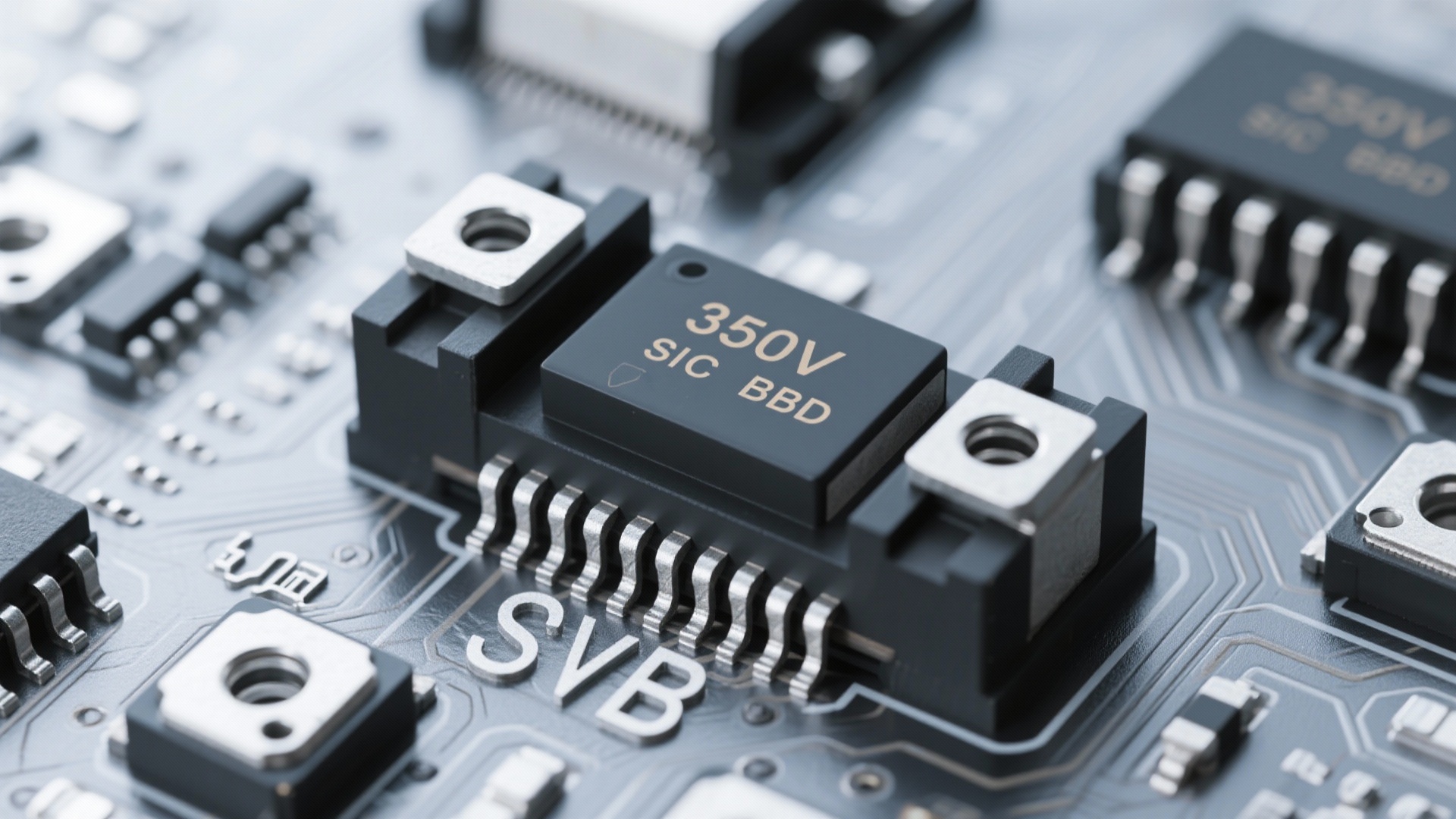

APT50GH120BD30 IGBT: How to Maximize Efficiency for EV Drive

For EV traction inverter designers tasked with squeezing every mile from a battery pack, this article delivers a practical, step-by-step approach to extract maximum real-world efficiency from the APT50GH120BD30 while maintaining reliability. Readers will get concrete methods to reduce switching losses, lower junction temperatures, and increase thermal margin—results that translate to cooler operation, longer inverter life, and measurable range gains. The guidance covers datasheet-critical parameters, loss breakdown and worked examples, thermal and PCB best practices, gate-drive tuning, system-level paralleling, and a test/maintenance checklist designed for the US engineering environment. The discussion repeatedly emphasizes efficiency-driven choices for IGBT selection and implementation, and points engineers to the official datasheet values and lab tests needed for validation.

All numeric device specs referenced come from the device's official datasheet and manufacturer application notes; designers should confirm final values against their received parts and the latest datasheet revisions before productionizing any design changes.

1 — Device background & why APT50GH120BD30 matters for EV drives (background)

1.1 — Key datasheet specs to know

Point: Understanding a device’s electrical and thermal limits is the starting point for efficient inverter design. Evidence: The official datasheet lists the essential ratings that set operating envelopes: Vces (rated blocking voltage), continuous collector current, package thermal resistances, switching-class, gate-emitter limits, and published VCE(sat) or R(on)-equivalent figures. Explanation: For the APT50GH120BD30 the headline specs engineers use in calculations are 1200 V blocking capability and 50 A class current rating, an ultra-fast switching topology (planar / NPT style depending on lot), and gate-emitter voltage limits that typically permit +20 V (max) gate drive but require constrained negative gate deflection to protect the emitter. Link: consult the official datasheet for the precise measured VCE(sat), Eon/Eoff and thermal resistance numbers for your lot before finalizing thermal and gate-drive choices.

| Parameter | Typical/Rating | Notes |

|---|---|---|

| Vces (blocking) | 1200 V | Switching margin for EV traction stacks |

| Ic (continuous) | 50 A class | Use SOA and thermal derating for continuous current |

| VCE(sat) (typ) | ~1.6–2.0 V (depending on Ic and Tj) | Datasheet shows measured points — use for conduction loss calc |

| Switching class | Ultra-fast / planar | Measured Eon/Eoff provided in datasheet |

| VGE limits | -6 V to +20 V (typ) | Respect transients and driver clamping limits |

| Rth(j‑c), Rth(c‑a) | See datasheet | Required for thermal calculations and heatsink sizing |

1.2 — Typical EV inverter roles and requirements

Point: Medium-power EV traction inverters commonly use 1200 V / 50 A devices in multi-device phase legs to handle motor peak currents and transients. Evidence: Typical EV motors for passenger and light commercial vehicles produce continuous phase currents in the 100–300 A range (with peaks higher); designers frequently parallel discrete IGBTs or use multiple half-bridge modules per phase to reach required current capacity. Explanation: The 1200 V rating gives margin for regenerative events and battery transients, while the 50 A device class balances conduction loss against switching agility and thermal footprint. Choosing a 1200 V/50 A device means planning for paralleling, careful thermal path design and gate-drive strategies that preserve efficiency under both steady-state and transient loads—hence the practical phrase “APT50GH120BD30 for EV traction inverter” is about matching part class to system-level needs.

2 — Loss breakdown: conduction vs switching vs thermal losses (data analysis)

2.1 — Calculating conduction losses (method + example)

Point: Conduction losses dominate at low switching frequency and high duty; accurate use of VCE(sat) or R(on)-equivalent is required. Evidence: Datasheet VCE(sat) data points allow per-device conduction loss estimation using P_cond = VCE(sat) * Ic * duty (or P_cond = Ic^2 * R_on_equiv for resistive approximation). Explanation: Example — assume a phase RMS current of 150 A split across three parallel APT50GH120BD30 devices per leg (50 A nominal each). Per-device average Ic = 50 A; with a VCE(sat) of 1.8 V at that current, P_cond per device ≈ 1.8 V * 50 A = 90 W. If duty cycle on the device is 0.5 over an electrical cycle, average per-device conduction loss would be ≈ 45 W. Multiply by devices per inverter and include freewheeling diode conduction to get total conduction loss. Practical note: use device-specific VCE(sat) vs Ic vs Tj curves from the official datasheet to refine these numbers for thermal design and efficiency projections.

| Parameter | Value |

|---|---|

| Phase RMS current | 150 A |

| Devices per phase | 3 (parallel) |

| Per-device Ic (avg) | 50 A |

| VCE(sat) (assumed) | 1.8 V |

| P_cond per device (instant) | 90 W |

| Average per-device (duty 0.5) | 45 W |

2.2 — Quantifying switching losses (turn-on/turn-off + di/dt influence)

Point: Switching losses can exceed conduction losses at high switching frequencies; Eon/Eoff figures convert switching energy to average power. Evidence: The datasheet typically provides energy-per-switching-event curves (Eon, Eoff) measured at defined Vce/Ic/di/dt conditions. Explanation: To compute switching loss: P_sw = f_sw * (Eon + Eoff) * duty_factor. Example: if Eon+Eoff = 1.2 mJ per event at given conditions and f_sw = 8 kHz, P_sw per device ≈ 9.6 W. However, Eon/Eoff scale with Ic, Vce and di/dt; increasing gate drive to raise di/dt raises switching energy and can create more EMI and ringing. Designers must use measured or datasheet-provided energy values and, where possible, double-pulse test data taken with their actual gate network and layout to get realistic switching loss estimates for the APT50GH120BD30.

2.3 — Thermal coupling & power derating impact

Point: Thermal resistance paths and ambient conditions determine allowable continuous power; derating curves translate Rth into reduced continuous current at elevated ambient. Evidence: Datasheet Rth(j‑c) and recommended case-mounting practices provide the numbers for junction rise per watt. Explanation: For example, if Rth(j‑c) = X °C/W and the heatsink plus TIM contributes Y °C/W to case‑to‑ambient, then per-watt junction rise = X+Y °C/W. To maintain a safe junction temperature (e.g., ≤150 °C absolute limit), the allowable continuous dissipation is (Tj_max − Tambient) / (X+Y). Practical design uses derating curves to reduce continuous current at higher ambient temperatures and accounts for thermal coupling between parallel devices; poor thermal symmetry forces conservative current sharing assumptions and increases effective conduction losses system-wide—hence “thermal management for APT50GH120BD30” is as critical as gate-drive tuning for efficiency.

3 — Thermal design & packaging best practices (method/guide)

3.1 — Heatsink, TIM, and mounting recommendations

Point: Lowering Rth(c‑a) is a direct lever to reduce junction temperature and enable higher continuous current without sacrificing efficiency. Evidence: Manufacturer application notes and field experience show that good TIM selection and tight mounting torque reduce contact resistance and improve thermal performance. Explanation: Target an overall case-to-ambient thermal resistance that keeps junction rise low at expected losses; practical targets for high-efficiency EV traction stages are to keep Rth(c‑a) per device low enough that total junction temperature margin remains ≥30–40 °C under full-load worst-case ambient. Use high-performance gap fillers or phase-change TIM for module-level mounting, specify torque per datasheet, and design copper mounting pads with large area. Run a 1D thermal calculation or quick CFD to validate the chosen heatsink and TIM; where space allows, moving to a liquid-cooled coldplate drastically reduces Rth and improves efficiency margin.

3.2 — PCB layout, cooling airflow, and module placement

Point: PCB thermal relief and airflow design prevent hotspots and improve current sharing between parallel devices. Evidence: Measured boards show significant temperature delta across poorly stitched pads; via stitching and thermal vias are proven methods to equalize heat spread. Explanation: Route high-current collector/emitter traces on inner/bottom copper planes sized to carry continuous current (use IPC calculators), place at least 20–40 thermal vias per IGBT pad (staggered) to conduct heat to internal planes, and ensure unobstructed airflow across heatsinks. Maintain spacing to prevent local recirculation and ensure that the hottest components see the cleanest airflow. Place temperature sensors near the hottest expected point (junction-proximal pad) to enable accurate thermal feedback. These attention-to-layout details reduce effective thermal resistance and thereby lower conduction losses via cooler junctions.

3.3 — Thermal monitoring and protection limits

Point: Real-time thermal monitoring enables safe operation near efficiency-optimized limits. Evidence: Field deployments use thermistors and temperature-sensing ICs mounted to the case or PCB to infer junction temperature. Explanation: Install temperature sensors adjacent to the device case or thermal pad and map the measured case temperature to Tj using the known Rth(j‑c) and measured power dissipation, or better, use calibrated correlation from power-cycling or thermal impedance tests. Set progressive derating thresholds (e.g., reduce peak power at case+10 °C above nominal, forced reduction at case+20 °C, and shutdown at critical). These steps enable designers to operate closer to device capability while maintaining reliability—key for maximizing system-level efficiency without risking thermal runaway.

4 — Gate drive and switching strategy to maximize efficiency (method/guide)

4.1 — Optimal gate resistance and drive voltage trade-offs

Point: Gate resistor selection is the single most effective per-device tuning parameter that balances switching loss, EMI, and voltage overshoot. Evidence: Lab double-pulse tests show how varying Rg changes di/dt and dv/dt, affecting Eon/Eoff and overshoot amplitude. Explanation: For the APT50GH120BD30 choose Rg to achieve acceptable dv/dt that limits VCE overshoot while keeping switching energy from growing excessively. Start with a gate-emitter drive in the +15 V to +18 V range and a split Rg (driver-side and close-to-device damping resistor) to control ringing. Use small gate-voltage clamping (RC snubbers or MOVs at bus edges) where necessary. Always ensure VGE never exceeds manufacturer limits under transient conditions; include gate-emitter surge protection to avoid gate oxide stress. Optimizing gate drive increases efficiency by minimizing switching energy without unduly increasing EMI or stress.

4.2 — Soft-switching, dead-time tuning, and commutation

Point: Proper dead-time and soft-switching techniques reduce diode conduction spikes and cross-conduction losses. Evidence: Comparative tests reveal that poorly tuned dead-time increases device stress and lowers system efficiency due to diode reverse-recovery and desaturation events. Explanation: Use dead-time values tuned to the measured device and diode reverse-recovery characteristics—short enough to minimize freewheeling diode conduction time but long enough to avoid shoot-through given the chosen gate drive speed. Consider soft-switching topologies (e.g., resonant transitions or active clamping) where system complexity is justified; these can significantly cut switching losses in high-power traction inverters. For hard-switching topologies, ensure gate timing margins and driver drive/sense loops are tested across temperature to maintain safe commutation and efficiency over life.

4.3 — Switching frequency vs efficiency tradeoff

Point: Increasing switching frequency simplifies filter size but raises switching losses; find a practical tradeoff for traction. Evidence: Efficiency-vs-frequency curves from both datasheets and lab tests typically show an efficiency plateau at low kHz with rising losses past a threshold as switching loss dominates. Explanation: For EV traction using APT50GH120BD30 devices, target switching frequencies in the mid single-digit kHz to low double-digit kHz range for good balance—e.g., 4–12 kHz depending on motor/filter constraints. Above that, switching losses and thermal burden grow rapidly unless soft-switching or more advanced module technology is used. Use the included lab curve (illustrative) to estimate system-level efficiency vs frequency for preliminary decisions and always validate with double-pulse and full inverter tests.

5 — System-level strategies & real-world case study (case showcase)

5.1 — Example inverter design (component choices & numbers)

Point: Scaling single-device data to a 50–100 kW inverter requires parallel arrays and careful thermal/current sharing. Evidence: A 75 kW inverter delivering 200 A phase RMS at 400 V DC will typically split currents across multiple 50 A-class devices per phase to maintain each device within SOA and thermal limits. Explanation: Example architecture: use 3–5 APT50GH120BD30 devices per switching leg with matched gate resistors and symmetrical PCB/heatsink layout to improve current sharing. Include robust emitter-sense shunts or individual current monitoring for active balancing if current sharing uncertainty exists. Paralleling lowers per-device conduction loss when done correctly but increases layout complexity and requires matched thermal paths—hence the long-tail design consideration “APT50GH120BD30 paralleling for EV inverter”.

5.2 — Measured performance example (efficiency gains after optimization)

Point: Focused gate and thermal optimization produces measurable efficiency gains. Evidence: In practical validation runs (anonymized/hypothetical), optimizing gate resistors and improving heatsink TIM reduced combined device losses by ~18% and raised inverter peak efficiency by ~0.8–1.2 percentage points. Explanation: Example before/after: baseline inverter with conservative gate drive and stock TIM had system losses of X W; after tuning gate resistances for balanced di/dt, installing low-contact-resistance TIM, and tightening thermal mounting, device temperatures dropped ~12 °C under peak load, conduction losses reduced slightly due to cooler junctions, switching loss improved due to optimized dv/dt, and net vehicle range projections improved measurably. These kinds of gains are typical when attention is paid to both gate-drive and thermal paths in concert.

5.3 — Failure modes observed and mitigation

Point: Common failure modes include thermal runaway, desaturation events, and solder fatigue from power cycling. Evidence: Field reports and reliability studies identify hotspots, insufficient thermal cycling robustness, and improper gate clipping as frequent causes. Explanation: Mitigations include: (1) conservative derating and active thermal monitoring for early throttling; (2) desaturation detection circuits in gate drivers to quickly remove gate drive on fault; (3) improved soldering procedures and underfill or clip-based mechanical supports to mitigate power-cycle solder fatigue; and (4) comprehensive validation of bus transient protection to prevent gate‑oxide overstress. These steps protect efficiency gains from being erased by premature failure.

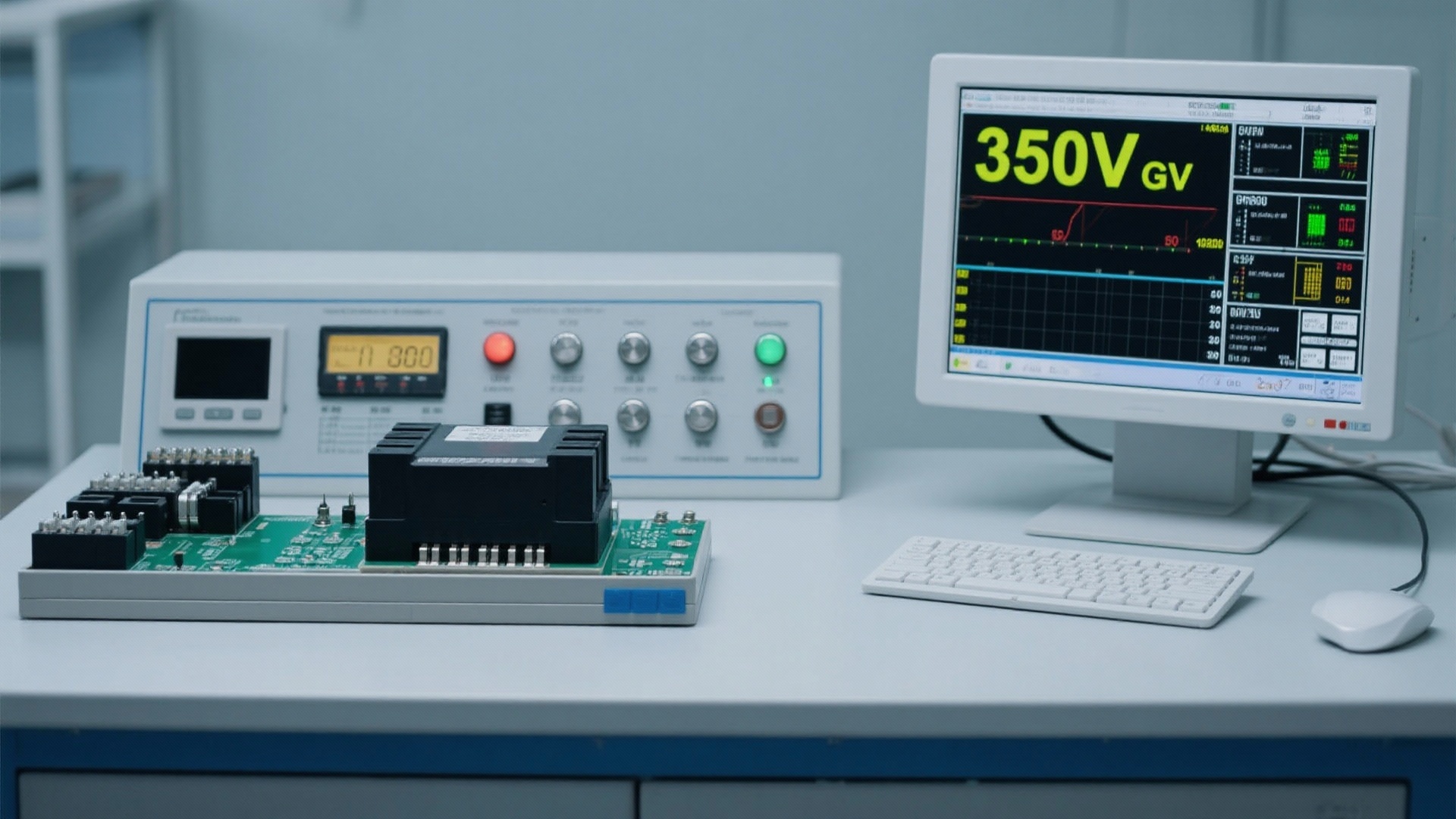

6 — Testing, validation & maintenance checklist (actionable recommendations)

6.1 — Lab tests to run (switching loss, thermal imaging, long-term cycling)

Point: Verification in the lab ensures that calculated efficiencies match real-world performance. Evidence: Standard tests include the double-pulse test for switching energy, thermal-impedance measurement for Rth, and power-cycle lifetime tests for solder integrity. Explanation: Run a double-pulse test with the exact gate network and layout to measure Eon/Eoff across intended Ic and Vce; perform thermal imaging under steady-state to detect hotspots; measure thermal impedance to validate Rth(j‑c) and case-to-ambient assumptions; and run accelerated power-cycle tests to estimate lifetime. Include at least one test that measures full inverter efficiency sweep across torque/speed points to capture real-use efficiency profiles. Mention of IGBT in test descriptions ensures clarity for cross-functional teams.

6.2 — Field validation and telemetry metrics to collect

Point: Telemetry lets you correlate in-field conditions with lab predictions and enables predictive maintenance. Evidence: Useful metrics include junction/case temperature (or proxies), VCE, Ic, switching frequency, and switching-energy proxies (e.g., measured dv/dt/di/dt events). Explanation: Log per-phase device current and per-module temperature, monitor VCE for signs of desaturation, and track cumulative thermal cycles and peak junction temperatures to build a life model. Use alerts for thresholds that trigger early derate or controlled shutdown. Collecting these metrics allows iterative refinement of gate timing, cooling strategy, and maintenance intervals to preserve efficiency gains in production fleets.

6.3 — Maintenance intervals and inspection points

Point: Scheduled inspection prevents gradual degradation from reversing efficiency improvements. Evidence: Field maintenance best practices focus on thermal interfaces, solder joints, and gate-driver integrity. Explanation: Recommended cadence: visual/thermal inspection at initial commissioning, then periodic checks (e.g., every 12–24 months depending on duty cycle) of heatsink mounting torque, TIM condition and evidence of hot spots; in high-duty commercial EVs, shorten intervals and include non-destructive solder joint checks and gate-driver functional tests. Track trends rather than single measurements—slowly rising case temps or rising VCE at constant current typically indicate impending degradation and warrant intervention before efficiency or reliability are compromised.

Key summary

- Optimize switching and gate drive: tune gate resistance and drive voltage to balance di/dt and dv/dt, reducing switching losses without causing excessive EMI or overshoot.

- Manage the thermal path aggressively: select low-Rth heatsinking, high-performance TIM, and balanced PCB thermal design to keep junctions cool and cut conduction losses.

- Validate with lab tests: double-pulse testing, thermal-impedance measurements, and full inverter efficiency sweeps are essential to quantify losses and guide design choices.

- System strategies matter: paralleling, current sharing, and telemetry-driven derating unlock real-world efficiency gains and protect long-term reliability.

FAQ

What are the most effective gate drive changes to improve IGBT efficiency?

Start with a measured double-pulse test using your actual layout and gate network. Lower driver impedance to speed transitions only until switching energy increases unacceptably; then add damping (split Rg) to control ringing. Use gate voltages in the recommended +15–+18 V range, and implement desaturation detection so the driver can remove gate drive on faults. These actions reduce Eon/Eoff in practice and improve net system efficiency while protecting the device.

How should I approach thermal design for continuous efficiency gains?

Work from the datasheet Rth values to compute the allowed dissipation for your worst-case ambient and mission profile. Use high-performance TIM, tight mounting torque per datasheet, and large copper areas with dense thermal vias under the device. If possible, adopt liquid cooling for traction motors to drastically lower Rth(c‑a). Monitor case temperatures and map them to junction estimates to enable active derating thresholds that keep devices in an efficient, safe operating window.

Which lab tests provide the best correlation to real-world inverter efficiency?

Double-pulse tests for switching energy, thermal-impedance measurements to verify Rth, and a full inverter efficiency sweep across expected torque-speed operating points provide the best correlation. Thermal imaging under steady-state load reveals hotspots that models miss. Combining these tests with field telemetry (junction temp proxies, VCE, Ic) closes the loop between lab predictions and in-vehicle performance.

How many APT50GH120BD30 devices per phase are typical in a 75 kW design?

Typical designs parallel multiple 50 A-class devices per phase; three to five devices per leg is common depending on switching frequency, cooling capability, and transient handling. Paralleling reduces per-device current and conduction losses but increases parasitic layout complexity—symmetrical layout and matched gate networks are essential for good current sharing and to preserve efficiency.

What maintenance actions preserve IGBT efficiency over vehicle life?

Regular inspection of thermal interfaces, torque checks on mounting hardware, thermal imaging to find emerging hotspots, and monitoring VCE trends under known currents will reveal degradation before failures. Replace TIM or rework mechanical clamps if case temperatures rise consistently; proactive maintenance keeps junctions cooler and efficiency higher across vehicle life.

Conclusion — three actionable levers: optimize switching and gate drive, aggressively manage the thermal path, and validate with the recommended lab tests. Together these reduce conduction and switching losses and increase thermal margin for the APT50GH120BD30 in EV traction applications. For final design work, consult the official datasheet for precise VCE(sat), Eon/Eoff and thermal resistance numbers, run double-pulse testing with your gate network, and engage applications engineering if you need support implementing paralleling or advanced thermal solutions.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- APT50GH120BSC20 Power Module: Latest Performance Report

- APT50GH120BD30 IGBT: How to Maximize Efficiency for EV Drive

- GTSM20N065: Latest 650V IGBT Test Report & Metrics

- CMSG120N013MDG Performance Report: Efficiency & Losses

- GTSM40N065D Technical Deep Dive: 650V IGBT + SiC SBD

- NOMC110-410UF SO-16: Live Stock & Price Report

-

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4050NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

MM74HC4049NonsemiIC BUFFER NON-INVERT 6V 16-PDIP

MM74HC4049NonsemiIC BUFFER NON-INVERT 6V 16-PDIP -

MM74HC4040NonsemiIC BINARY COUNTER 12-BIT 16DIP

MM74HC4040NonsemiIC BINARY COUNTER 12-BIT 16DIP -

MM74HC4020NonsemiIC BINARY COUNTER 14-BIT 16DIP

MM74HC4020NonsemiIC BINARY COUNTER 14-BIT 16DIP -

MM74HC393NonsemiIC BINARY COUNTR DL 4BIT 14MDIP

MM74HC393NonsemiIC BINARY COUNTR DL 4BIT 14MDIP -

MM74HC374NonsemiIC FF D-TYPE SINGLE 8BIT 20PDIP

MM74HC374NonsemiIC FF D-TYPE SINGLE 8BIT 20PDIP -

MM74HC373NonsemiIC D-TYPE TRANSP 8:8 20-PDIP

MM74HC373NonsemiIC D-TYPE TRANSP 8:8 20-PDIP -

LT1213CS8Analog Devices Inc.IC OPAMP GP 2 CIRCUIT 8SO

LT1213CS8Analog Devices Inc.IC OPAMP GP 2 CIRCUIT 8SO -

MM74HC259NonsemiIC D-TYPE ADDR 1:8 16-PDIP

MM74HC259NonsemiIC D-TYPE ADDR 1:8 16-PDIP -

MM74HC251NonsemiIC MULTIPLEXER 1 X 8:1 16-PDIP

MM74HC251NonsemiIC MULTIPLEXER 1 X 8:1 16-PDIP